第四章:利用逻辑门巧妙搭建,理解计算机加法逻辑

半加器

如何通过第四章第一节‘半加器’? - TapTap

https://www.taptap.com/topic/19180148?share_id=5f07b3e774b1&utm_medium=share&utm_source=copylink

全加器

如何通关第四章第二节‘全加器’? - TapTap

https://www.taptap.com/topic/19183036?share_id=3d3289f8b082&utm_medium=share&utm_source=copylink

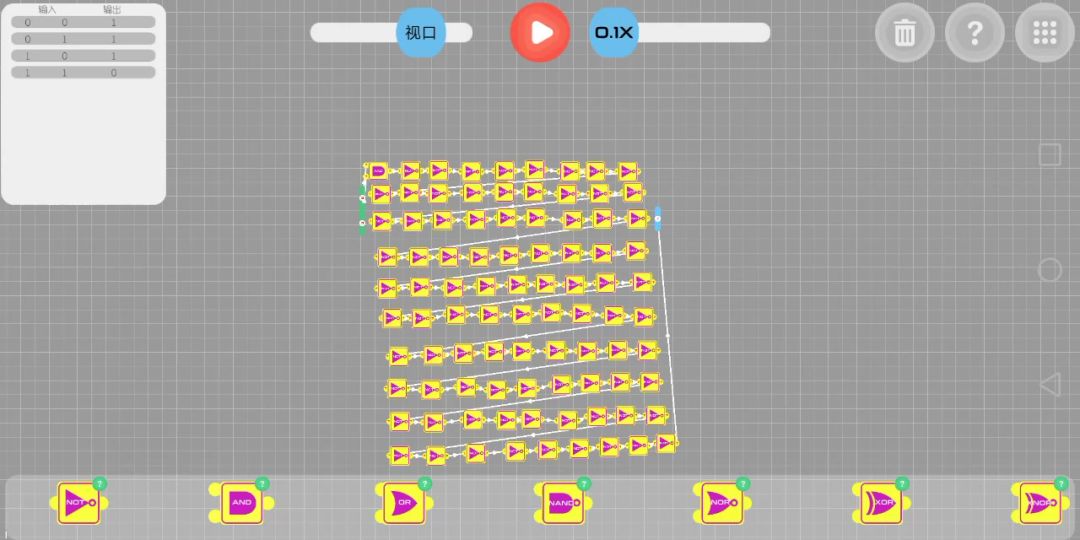

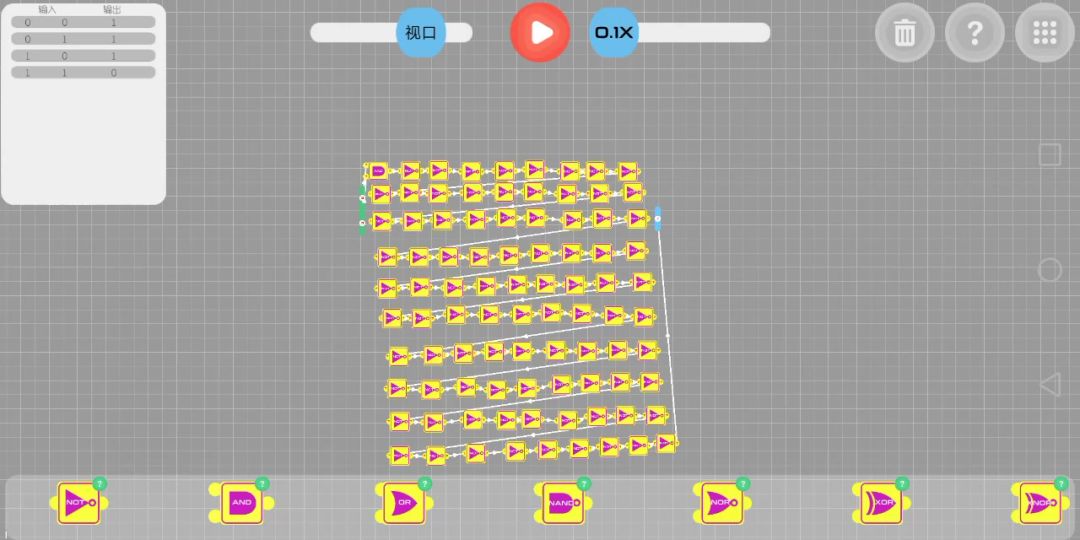

2位加法器

4位加法器

https://www.bilibili.com/read/mobile?id=11208028